### **Features**

- 7 Full Decades of Range: 1 nA to 10 mA

- Functionally Support 100-pA Current Input

- Low Conformance Error: 0.2 dB from 10 nA to 10 mA

- Fast Step Response: Raising 0.2 μs, Falling 5 μs for 10-nA to 10-μA Input on INPT

- · Basic Logarithmic Intercept at 100 pA

- Logarithmic Slope of 200 mV/20 dB (at the V<sub>LOG</sub> Pin)

- · Optimized for Fiber Optic Photodiode Interfacing

- Single-Supply Operation: 4.5 V to 5.5 V

- Power-down Mode

## **Applications**

- High-Accuracy Optical Power Measurement

- Wide-Range Baseband Log Compression

- Versatile Detector for APC Loops

- EDFA

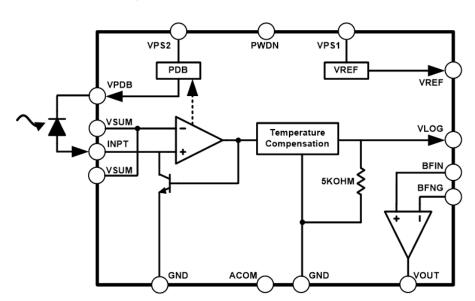

### **Description**

The TPA8304 is a logarithmic detector optimized for the measurement of low-frequency signal power in fiber optic systems and offers a large dynamic range.

The wide measurement range, accuracy, and fast step response are achieved, which meets the requirements of an optic system.

The TPA8304 requires only a single positive supply of 5 V. The low quiescent current and chip disable facilitate are used in battery-operated applications.

## **Typical Application Circuit**

## **Table of Contents**

| Features                                |    |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Typical Application Circuit             | 1  |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Specifications                          | 5  |

| Absolute Maximum Ratings <sup>(1)</sup> | 5  |

| ESD, Electrostatic Discharge Protection | 5  |

| Thermal Information                     | 5  |

| Electrical Characteristics              | 6  |

| Typical Performance Characteristics     | 8  |

| Application and Implementation          | 9  |

| Application Information                 | 9  |

| Typical Application                     | 11 |

| Tape and Reel Information               | 12 |

| Package Outline Dimensions              | 13 |

| TSSOP14                                 | 13 |

| QFN3X3-16                               | 14 |

| Order Information                       | 15 |

| IMPORTANT NOTICE AND DISCLAIMER         | 16 |

## **Revision History**

| Date       | Revision  | Notes                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2019-09-10 | Rev.Pre.0 | Initial version.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2019-12-09 | Rev.Pre.1 | Added a new section in Application Information: Using the Fixed Bias.                                                                                                                                                                                                                                                                                                                                                      |

| 2020-11-16 | Rev.A.0   | Added the Phase Margin and Gain Margin in Output Buffer, Pin BFIN, BFNG, V <sub>OUT</sub> in Electrical Characteristics.                                                                                                                                                                                                                                                                                                   |

| 2021-05-30 | Rev.A.1   | Updated the Description.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2025-10-10 | Rev.A.2   | The following updates are all about the new datasheet formats or typos, and the actual product remains unchanged.  Updated to a new datasheet format.  Updated to a new format of Package Outline Dimensions.  Updated EC Tables:  Update the Min and Max value of Intercept.  Update the typical value of Minimum Output Voltage.  Update the typical value of Output Voltage Swing to Power and Ground.  Update Figures. |

www.3peak.com 3 / 16 AA20251106A2

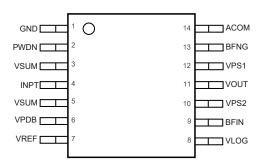

## **Pin Configuration and Functions**

TPA8304 TSSOP14 Top View

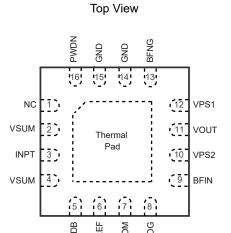

TPA8304

QFN3x3-16

Table 1. Pin Functions: TPA8304

| Pin     | No.       |                  |     | <b>5</b>                                                                                                                                 |

|---------|-----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP14 | QFN3x3-16 | Name             | I/O | Description                                                                                                                              |

| 1       | 14, 15    | GND              |     | Power supply ground connection.                                                                                                          |

| 2       | 16        | PWDN             | -   | Power-down control input. The device is active when PWDN is taken low.                                                                   |

| 3, 5    | 2, 4      | VSUM             |     | Guard pins. They are used to shield the INPT current line.                                                                               |

| 4       | 3         | INPT             | I   | Photodiode current input.                                                                                                                |

| 6       | 5         | VPDB             | 0   | Photodiode bias output. Connect this pin to the photodiode cathode when using adaptive bias control; Otherwise, leave this pin floating. |

| 7       | 6         | VREF             | 0   | Voltage reference output of 2 V.                                                                                                         |

| 8       | 8         | VLOG             | 0   | Output of the logarithmic front-end processor.                                                                                           |

| 9       | 9         | BFIN             | I   | Buffer amplifier non-inverting input.                                                                                                    |

| 10      | 10        | VPS2             |     | Positive supply.                                                                                                                         |

| 11      | 11        | V <sub>OUT</sub> | 0   | Buffer amplifier output.                                                                                                                 |

| 12      | 12        | VPS1             |     | Positive supply.                                                                                                                         |

| 13      | 13        | BFNG             | I   | Buffer amplifier inverting input.                                                                                                        |

| 14      | 7         | ACOM             |     | Analog reference ground.                                                                                                                 |

| -       | 1         | NC               |     | The pins labeled NC can be allowed to float, but it is better to connect these pins to ground.                                           |

| -       | -         | Thermal<br>Pad   |     | Thermal pad. Connect the thermal pad to the V <sub>SUM</sub> pin to provide low leakage guard.                                           |

www.3peak.com 4 / 16 AA20251106A2

## **Specifications**

### Absolute Maximum Ratings (1)

|                  | Parameter                            | Min | Max | Unit |

|------------------|--------------------------------------|-----|-----|------|

|                  | Supply Voltage                       |     | 6.5 | V    |

|                  | Input Current to INPT (2)            | -20 | 20  | mA   |

| TJ               | Maximum Junction Temperature         |     | 125 | °C   |

| T <sub>A</sub>   | Operating Temperature Range          | -40 | 85  | °C   |

| T <sub>STG</sub> | Storage Temperature Range            | -65 | 150 | °C   |

| TL               | Lead Temperature (Soldering, 10 sec) |     | 260 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter                | Condition                                                          | Minimum Level | Unit     |

|--------|--------------------------|--------------------------------------------------------------------|---------------|----------|

| НВМ    | Human Bada Madal 500     | ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> , INPT<br>Pin                | 500           | <b>V</b> |

|        | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> , All Other Pins except INPT | 2             | kV       |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2)                                         | 1             | kV       |

| LU     | Latabilia                | 25 degrees                                                         | 200           | mA       |

|        | Latch Up                 | 125 degrees                                                        | 150           | mA       |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### Thermal Information

| Package Type | θја | θυς | Unit |

|--------------|-----|-----|------|

| QFN3x3-16    | 75  | 54  | °C/W |

| TSSOP14      | 180 | 35  | °C/W |

www.3peak.com 5 / 16 AA20251106A2

<sup>(2)</sup> The inputs are protected by ESD protection diodes to each power supply. If the input extends more than 300 mV beyond the power supply, the input current should be limited to less than 10 mA.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Electrical Characteristics**

All test conditions:  $V_S = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted.

| Symbol    | Parameter                                            | Conditions                         | TA            | Min  | Тур   | Max  | Unit       |

|-----------|------------------------------------------------------|------------------------------------|---------------|------|-------|------|------------|

| Power S   | upply, Pin V <sub>PS2</sub> , V <sub>PS1</sub> , GND |                                    | 1             |      |       |      |            |

| Vs        | Supply Voltage Range                                 |                                    |               | 4.5  |       | 5.5  | V          |

| IQ        | Quiescent Current per Amplifier                      |                                    |               |      | 8     | 10   | mA         |

| Isn       | Shutdown Current                                     | In disable state                   |               |      | 40    |      | μA         |

| Input Int | erface, Pin INPT, V <sub>SUM</sub>                   |                                    |               |      |       |      |            |

|           | Specified Current Range                              | Flows toward INPT                  |               | 1    |       |      | nA         |

|           | Specified Current Nange                              | Flows toward live i                |               |      | 10    | 12   | mA         |

|           | Functional Current Range (1)                         | Flows toward INPT                  |               |      | 100   |      | pА         |

|           | Input Node Voltage                                   |                                    |               | 1.05 | 1.2   | 1.35 | V          |

|           | Input Node Voltage Drift                             |                                    |               |      | 20    |      | μV/°C      |

|           | V <sub>INPT</sub> - V <sub>SUM</sub>                 |                                    |               | -20  |       | 20   | mV         |

| Photodic  | ode Bias, between Pin V <sub>PDB</sub> and I         | NPT                                |               |      |       |      |            |

|           | Minimum Value                                        | IPD = 100 pA                       |               |      | 100   |      | mV         |

|           | Transresistance                                      |                                    |               |      | 150   |      | mV/m<br>A  |

| Logarith  | mic Output, Pin V <sub>LOG</sub>                     |                                    |               |      |       |      |            |

|           | Slope                                                |                                    |               | 195  | 200   | 205  | mV/de<br>c |

|           |                                                      |                                    | 0°C to 70°C   | 192  |       | 208  | mV/de      |

|           | Intercept                                            |                                    | 0°C to 70°C   | 75   | 100   | 125  | pА         |

|           |                                                      |                                    | -40°C to 85°C | 65   |       | 135  | pA         |

|           | Low Conformance Error                                | 10 nA < IPD < 10 mA,<br>peak error |               |      | 0.2   | 0.25 | dB         |

|           |                                                      | 1 nA < IPD < 10 mA,<br>peak error  |               |      | 0.5   | 0.75 | dB         |

|           | Maximum Output Voltage                               | IPD = 10 mA                        |               |      | 1.6   |      | ٧          |

|           | Minimum Output Voltage                               | IPD ≤ 100 pA                       |               |      | 0.002 |      | ٧          |

|           | Output Resistance                                    |                                    |               | 4.95 | 5     | 5.05 | kΩ         |

| Reference | ce Output, Pin V <sub>REF</sub>                      |                                    |               |      | '     | •    |            |

|           | Output Voltage                                       |                                    |               | 1.96 | 2     | 2.04 | ٧          |

|           |                                                      |                                    | -40°C to 85°C | 1.95 |       | 2.05 | ٧          |

|           | Output Resistance                                    |                                    |               |      | 2     |      | Ω          |

| Output E  | Buffer, Pin BFIN, BFNG, Vout                         |                                    |               |      |       |      |            |

| Vos       | Input Offset Voltage                                 |                                    |               | -10  |       | 10   | mV         |

|           |                                                      |                                    |               |      |       |      |            |

www.3peak.com 6 / 16 AA20251106A2

| Symbol         | Parameter                                | Conditions                      | TA            | Min | Тур | Max | Unit       |

|----------------|------------------------------------------|---------------------------------|---------------|-----|-----|-----|------------|

| I <sub>B</sub> | Input Bias Current                       |                                 |               |     | 100 |     | pА         |

|                | Output Voltage Swing to Power and Ground | No Load                         |               |     | 3   |     | mV         |

|                | Output Resistance                        |                                 |               |     | 0.5 |     | Ω          |

|                | Wideband Noise                           |                                 |               |     | 1   |     | μV/<br>√Hz |

|                | Small-Signal Bandwidth                   |                                 |               |     | 10  |     | MHz        |

| SR             | Slew Rate                                | 0.2-V to 4.8-V output swing     |               |     | 15  |     | V/µs       |

| РМ             | Phase Margin                             | C <sub>L</sub> = 100 pF         |               |     | 60  |     | 0          |

| GM             | Gain Margin                              | C <sub>L</sub> = 100 pF         |               |     | 10  |     | dB         |

| Power-d        | own Input, Pin PWDN                      |                                 |               |     |     |     |            |

|                | Logic Level, High State                  | V <sub>S</sub> = 4.5 V to 5.5 V | -40°C to 85°C | 2   |     |     | V          |

|                | Logic Level, Low State                   | V <sub>S</sub> = 4.5 V to 5. 5V | -40°C to 85°C |     |     | 1   | V          |

<sup>(1)</sup> Provided by the design simulation.

| Step Response Time from Input to V <sub>LOG</sub> , 0°C to 70°C |     |             |     |     |              |     |      |  |

|-----------------------------------------------------------------|-----|-------------|-----|-----|--------------|-----|------|--|

|                                                                 |     | Rising Time |     |     | Falling Time |     |      |  |

| Conditions                                                      | Min | Тур         | Max | Min | Тур          | Max | Unit |  |

| 10 nA to 100 nA                                                 |     | 2           |     |     | 4            |     | μs   |  |

| 10 nA to 1 μA                                                   |     | 0.5         |     |     | 3            |     | μs   |  |

| 10 nA to 10 μA                                                  |     | 0.2         |     |     | 5            |     | μs   |  |

| 10 nA to 100 μA                                                 |     | 0.2         |     |     | 10           |     | μs   |  |

| 10 nA to 1 mA                                                   |     | 0.2         |     |     | 15           |     | μs   |  |

www.3peak.com 7 / 16 AA20251106A2

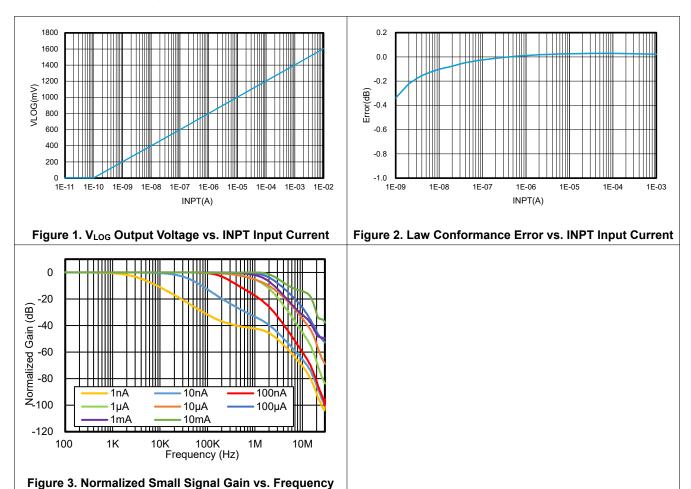

### **Typical Performance Characteristics**

All test conditions:  $V_S = 5 V$ , unless otherwise noted.

www.3peak.com 8 / 16 AA20251106A2

### **Application and Implementation**

#### Note

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### **Application Information**

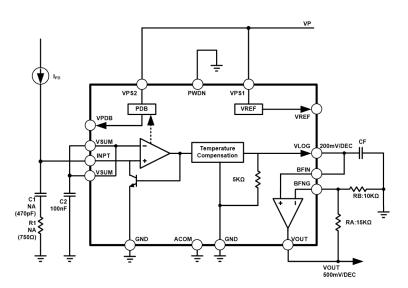

### **Basic Configuration to Use the TPA8304**

The basic configuration (see Figure 4) includes a 2.5x gain to amplify the  $V_{LOG}$  voltage by the buffer amplifier. This increases the slope of 10 mV/dB (200 mV/dec) at the  $V_{LOG}$  pin to 25 mV/dB (500 mV/dec) at  $V_{OUT}$ . For the full dynamic range of 140 dB, the output swing is 4.0 V, which can be accommodated by the rail-to-rail output stage when using the recommended 5-V supply.

The capacitor C1 and R1 at the INPT pin is not recommended to be assembled, because the TPA8304 uses advanced technology to ensure loop stability and fast step response. If C1 and R1 must be used to the ADI ADL5303 and AD8304 for compatibility, the recommended value is 470 pF for C1 and 750  $\Omega$  for R1, which can ensure larger output noise and slower step response than the unassembled configuration. The capacitor C<sub>F</sub> from V<sub>LOG</sub> to GND forms an optional single-pole low-pass filter. Since the resistance at this pin is 5 k $\Omega$ , a corner frequency of  $\neg$ 3-dB can be realized to minimize output noise. A capacitor between V<sub>SUM</sub> and GND is essential for minimizing the noise on this node. When the bias voltage at either V<sub>PDB</sub> or V<sub>REF</sub> is unnecessary, these pins should be left unconnected.

Figure 4. Basic Configuration

The relationship between the input current, IPD, applied to the INPT pin, and the voltage appearing at the V<sub>LOG</sub> pin is:

$$V_{LOG} = V_{Y} \times LOG_{10} \left( \frac{I_{PD}}{I_{Z}} \right)$$

(1)

### Where:

V<sub>Y</sub> is the voltage slope (in the case of base-10 logarithms, it is also referred to as volts per decade).

$I_Z$  is the fixed current in the logarithmic equation called the intercept.

www.3peak.com 9 / 16 AA20251106A2

In the basic configuration, the scaling is chosen so that  $V_Y$  is trimmed to 200 mV/decade (10 mV/dB). The intercept is positioned at 100 pA, and the output voltage,  $V_{LOG}$ , crosses zero when  $I_{PD}$  is of this value. However, the actual  $V_{LOG}$  must always be slightly above ground. Using Equation 1, the output for any value of  $I_{PD}$  can be calculated. For the specified input current of 1 nA to 10 mA of INPT:

$1 \text{ nA} : V_{LOG} = 0.2 \text{ V LOG}_{10} (1 \text{ nA}/100 \text{ pA}) = 0.2 \text{ V}$

10 mA:  $V_{LOG} = 0.2 \text{ V LOG}_{10} (10 \text{ mA}/100 \text{ pA}) = 1.6 \text{ V}$

In practice, both the slope and intercept can be altered, to either higher or lower values, without any significant loss of calibration accuracy, by using one or two external resistors, often in conjunction with the 2-V voltage reference at the  $V_{REF}$  pin.

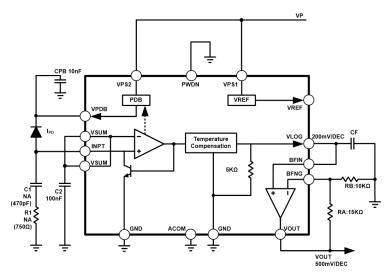

### **Using the Adaptive Bias**

For most photodiode applications, the placement of the anode above ground is acceptable in some cases, as long as the positive bias on the cathode is enough to support the peak current for a particular diode, limited by its series resistance. To address this matter, the TPA8304 provides a diode bias that increases linearly with the input current. This bias voltage appears at the  $V_{PDB}$  pin, and varies from 1.3 V (reverse-biasing the diode by 0.1 V) for  $I_{PD}$  = 100 pA and rises to 2.8 V (for a diode bias of 1.7 V) at  $I_{PD}$  = 10 mA. The adaptive biasing function is valuable in minimizing the dark current while preventing the loss of photodiode bias at high currents. The use of the adaptive bias feature is shown in Figure 5.

The capacitor  $C_{PB}$ , between the photodiode cathode at the  $V_{PDB}$  pin and GND, is used to lower the impedance at this node and improve the high-frequency accuracy at current levels where the bandwidth of the TPA8304 is high.  $C_{PB}$  also provides a high-frequency path for any high-frequency modulation on the optical signal. A suitable  $C_{BP}$  value (1 nF to 33 nF) is recommended in practice for the fast-falling step response. An undershoot appears at the output in the  $V_{LOG}$  pin when inputting a large-falling step (for example, 1 mA to 1 nA) if a large CPB value (> 33 nF) is used.

Figure 5. Using the Adaptive Bias

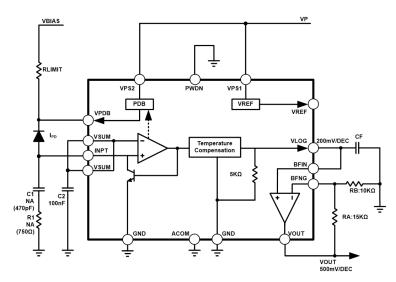

#### **Using the Fixed Bias**

For some photodiode applications, the fixed bias voltage is used for a photodiode. As the INPT pin has an around 1.2-V voltage, the voltage cross the photodiode must be carefully considered, especially during power-off or power-on of the chip. The current of the photodiode must be limited to the value of the rating current, otherwise, the photodiode may be damaged by the large current, (see Figure 6). To keep the photodiode safe, the system design should be guaranteed:

- Always keep the voltage of  $V_{BIAS}$  equal to or larger than  $V_P$  (the power supply of the TPA8304), especially during power-off or power-on. The same source for  $V_{BIAS}$  and  $V_P$  is recommended.

- Or, use the resistor R<sub>LIMIT</sub> to limit the current of the photodiode to a afe value if the previous solution is unavailable.

www.3peak.com 10 / 16 AA20251106A2

Figure 6. Using the Fixed Bias

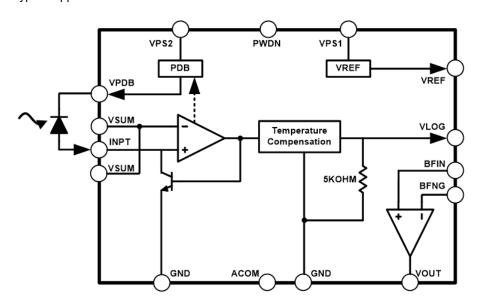

### **Typical Application**

Figure 7 shows the typical application schematic.

Figure 7. Typical Application Circuit

www.3peak.com 11 / 16 AA20251106A2

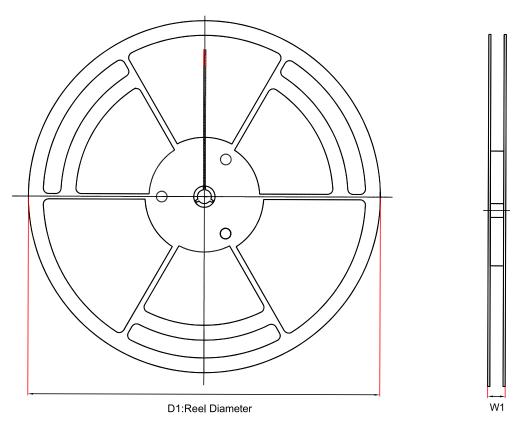

# **Tape and Reel Information**

| Order Number   | Package   | D1 (mm) | W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | W0<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------|---------|------------|------------|------------|------------|------------|------------|------------------|

| TPA8304-TS2R-S | TSSOP14   | 330     | 17.6       | 6.8        | 5.5        | 1.5        | 8          | 12         | Q1               |

| TPA8304-QF4R   | QFN3X3-16 | 330     | 16.6       | 3.2        | 3.2        | 1.1        | 8          | 12         | Q1               |

| TPA8304-QF4R-S | QFN3X3-16 | 330     | 16.6       | 3.2        | 3.2        | 1.1        | 8          | 12         | Q1               |

www.3peak.com 12 / 16 AA20251106A2

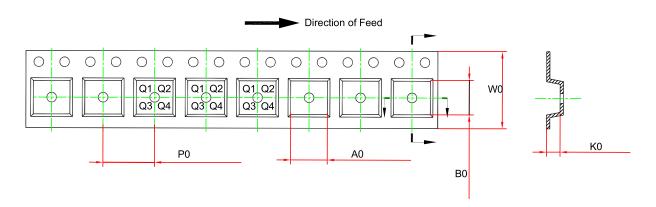

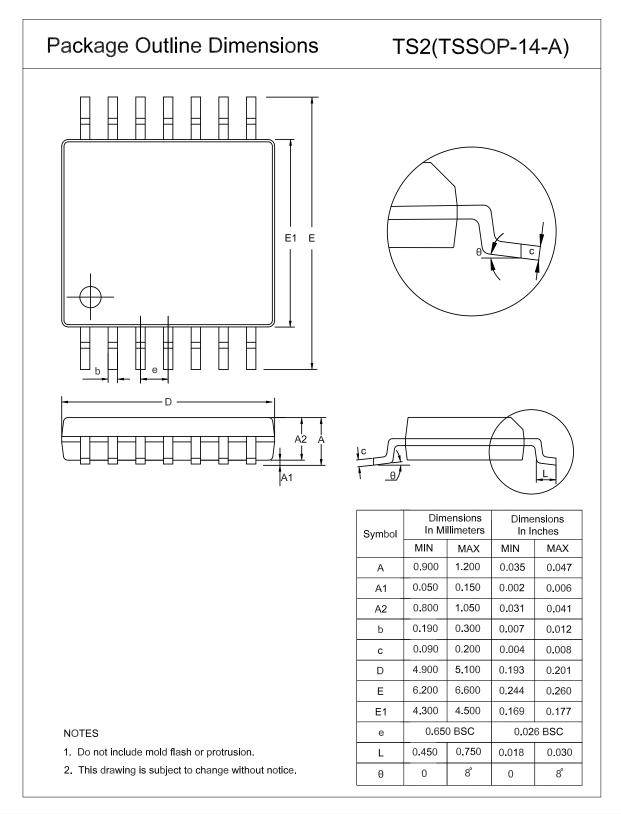

## **Package Outline Dimensions**

### TSSOP14

### QFN3X3-16

### **Order Information**

| Order Number   | Operating Temperature Range | Package   | Marking Information | MSL | Transport Media, Quantity | Eco Plan |

|----------------|-----------------------------|-----------|---------------------|-----|---------------------------|----------|

| TPA8304-TS2R-S | −40 to 85°C                 | TSSOP14   | A8304               | 3   | Tape and Reel, 3000       | Green    |

| TPA8304-QF4R   | -40 to 85°C                 | QFN3×3-16 | A8304               | 3   | Tape and Reel, 4000       | Green    |

| TPA8304-QF4R-S | -40 to 85°C                 | QFN3×3-16 | A8304               | 3   | Tape and Reel, 4000       | Green    |

**Green**: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

www.3peak.com 15 / 16 AA20251106A2

### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2025. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.

www.3peak.com 16 / 16 AA20251106A2