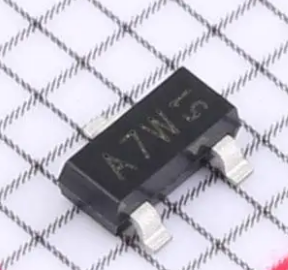

General Description:

Altera's FLEX 10K devices are the industry’s first embedded PLDs. Based on reconfigurable CMOS SRAM elements, the Flexible Logic Element MatriX (FLEX) architecture incorporates all features necessary to implement common gate array megafunctions. With up to 250,000 gates, the FLEX 10K family provides the density, speed, and features to integrate

entire systems, including multiple 32-bit buses, into a single device.FLEX 10K devices are reconfigurable, which allows 100% testing prior to shipment. As a result, the designer is not required to generate test vectors for fault coverage purposes. Additionally, the designer does not need to manage inventories of different ASIC designs; FLEX 10K devices can be configured on the board for the specific functionality required.

Features:

■ The industry’s first embedded programmable logic device (PLD) family, providing System-on-a-Programmable-Chip (SOPC) integration

– Embedded array for implementing megafunctions, such as efficient memory and specialized logic functions

– Logic array for general logic functions

■ High density

– 10,000 to 250,000 typical gates (see Tables 1 and 2)

– Up to 40,960 RAM bits; 2,048 bits per embedded array block (EAB), all of which can be used without reducing logic capacity

■ System-level features

– MultiVoltTM I/O interface support

– 5.0-V tolerant input pins in FLEX® 10KA devices

– Low power consumption (typical specification less than 0.5 mA in standby mode for most devices)

– FLEX 10K and FLEX 10KA devices support peripheral component interconnect Special Interest Group (PCI SIG) PCI

Local Bus Specification, Revision 2.2

– FLEX 10KA devices include pull-up clamping diode, selectable on a pin-by-pin basis for 3.3-V PCI compliance

– Select FLEX 10KA devices support 5.0-V PCI buses with eight or fewer loads

– Built-in Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990, available without consuming any device logic

Flexible interconnect

– FastTrack® Interconnect continuous routing structure for fast, predictable interconnect delays

– Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

– Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions)

– Tri-state emulation that implements internal tri-state buses

– Up to six global clock signals and four global clear signals

■ Powerful I/O pins

– Individual tri-state output enable control for each pin

– Open-drain option on each I/O pin

– Programmable output slew-rate control to reduce switching noise

– FLEX 10KA devices support hot-socketing

■ Peripheral register for fast setup and clock-to-output delay

■ Flexible package options

– Available in a variety of packages with 84 to 600 pins (see Tables 4 and 5)

– Pin-compatibility with other FLEX 10K devices in the same package

– FineLine BGATM packages maximize board space efficiency

■ Software design support and automatic place-and-route provided by Altera development systems for Windows-based PCs and Sun SPARCstation, HP 9000 Series 700/800 workstations

■ Additional design entry and simulation support provided by EDIF 200 and 300 netlist files, library of parameterized modules (LPM), DesignWare components, Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, VeriBest, and Viewlogic.

MCU Solutions

MCU Solutions PCBA Solutions

PCBA Solutions Bluetooth Solutions

Bluetooth Solutions

FAQ

FAQ Contact Us

Contact Us

Company News

Company News Technology News

Technology News Industry News

Industry News

Company Profile

Company Profile Certificates

Certificates Terms & Conditions

Terms & Conditions Privacy Statement

Privacy Statement

Home Appliances

Home Appliances Beauty Appliances

Beauty Appliances Lighting

Lighting Kid's Toys

Kid's Toys Security Alarm

Security Alarm Health Care

Health Care