Introduction:

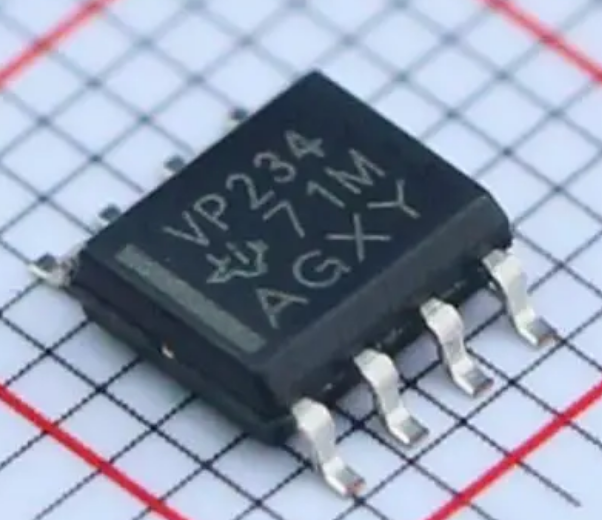

This data sheet describes the functionality of the CLRC632 Integrated Circuit (IC). Itincludes the functional and electrical specifications and from a system and hardwareviewpoint gives detailed information on how to design-in the device.Remark: The CLRC632 supports all variants of the MIFARE Mini, MIFARE 1K,MIFARE 4K and MIFARE Ultralight RF identification protocols. To aid readabilitythroughout this data sheet, the MIFARE Mini, MIFARE 1K, MIFARE 4K andMIFARE Ultralight products and protocols have the generic name MIFARE.

General description:

The CLRC632 is a highly integrated reader IC for contactless communication at13.56 MHz. The CLRC632 reader IC provides:

• outstanding modulation and demodulation for passive contactless communication

• a wide range of methods and protocols

• a small, fully integrated package

• pin compatibility with the MFRC500, MFRC530, MFRC531 and SLRC400All protocol layers of the ISO/IEC 14443 A and ISO/IEC 14443 B communicationstandards are supported provided:

• additional components, such as the oscillator, power supply, coil etc. are correctlyapplied.

• standardized protocols, such as ISO/IEC 14443-4 and/or ISO/IEC 14443 Banticollision are correctly implemented

Features and benefits:

Highly integrated analog circuitry for demodulating and decoding card/label response

Buffered output drivers enable antenna connection using the minimum of externalcomponents

Proximity operating distance up to 100 mm

Supports both ISO/IEC 14443 A and ISO/IEC 14443 B standards

Supports MIFARE dual-interface card ICs and the MIFARE Mini, MIFARE 1K,MIFARE 4K protocols

Contactless communication at MIFARE higher baud rates (up to 424 kBd)

Supports both I-CODE1 and ISO/IEC 15693 protocols

Crypto1 and secure non-volatile internal key memory

Pin-compatible with the MFRC500, MFRC530, MFRC531 and the SLRC400

Parallel microprocessor interface with internal address latch and IRQ line

SPI compatibility

Flexible interrupt handling

Automatic detection of parallel microprocessor interface type

64-byte send and receive FIFO buffer

Hard reset with low power function

Software controlled Power-down mode

Programmable timer

Unique serial number

User programmable start-up configuration

Bit-oriented and byte oriented framing

Independent power supply pins for analog, digital and transmitter modules

Internal oscillator buffer optimized for low phase jitter enables 13.56 MHz quartzconnection

Clock frequency filtering

3.3 V to 5 V operation for transmitter in short range and proximity applications

3.3 V or 5 V operation for the digital module

Applications:

Electronic payment systems

Identification systems

Access control systems

Subscriber services

Banking systems

Digital content systems

MCU Solutions

MCU Solutions PCBA Solutions

PCBA Solutions Bluetooth Solutions

Bluetooth Solutions

FAQ

FAQ Contact Us

Contact Us

Company News

Company News Technology News

Technology News Industry News

Industry News PCBA News

PCBA News

Company Profile

Company Profile Certificates

Certificates Terms & Conditions

Terms & Conditions Privacy Statement

Privacy Statement

Home Appliances

Home Appliances Beauty Appliances

Beauty Appliances Lighting

Lighting Kid's Toys

Kid's Toys Security Alarm

Security Alarm Health Care

Health Care