Description:

The PY25R128LA is a serial interface Flash memory device designed for use in a wide variety of high-volume

consumer-based applications in which program code is shadowed from Flash memory into embedded or

external RAM for execution. The flexible erase architecture of the device, with its page erase granularity it is

ideal for data storage as well, eliminating the need for additional data storage devices.

The erase block sizes of the device have been optimized to meet the needs of today's code and data storage

applications. By optimizing the size of the erase blocks, the memory space can be used much more efficiently.

Because certain code modules and data storage segments must reside by themselves in their own erase

regions, the wasted and unused memory space that occurs with large sectored and large block erase Flash

memory devices can be greatly reduced. This increased memory space efficiency allows additional code

routines and data storage segments to be added while still maintaining the same overall device density.

The device also contains an additional 3*1024-byte security registers with OTP lock (One-Time

Programmable), can be used for purposes such as unique device serialization, system-level Electronic Serial

Number (ESN) storage, locked key storage, etc.

Specifically designed for use in many different systems, the device supports read, program, and erase

operations with a wide supply voltage range of 1.65V to 2.0V. No separate voltage is required for

programming and erasing.

The PY25R series is also equipped with an enhanced authentication security feature by Replay Protection

Monotonic Counter (RPMC). It provides a high level secured communication between the flash device and the

controller to detect Hardware attack.

Overview:

General:

Single 1.65 to 2.0V supply

Industrial Temperature Range -40C to 85C

Serial Peripheral Interface (SPI) Compatible: Mode 0 and Mode 3

Single, Dual, Quad SPI, QPI, DTR

- Standard SPI: SCLK, CS#, SI, SO

- Dual SPI: SCLK, CS#, IO0, IO1

- Quad SPI: SCLK, CS#, IO0, IO1, IO2, IO3

- QPI: SCLK, CS#, IO0, IO1, IO2, IO3

- DTR: Double Transfer Rate Read

Flexible Architecture for Code and Data Storage

- Uniform 256-byte Page Program

- Uniform 4K-byte Sector Erase

- Uniform 32K/64K-byte Block Erase

- Full Chip Erase

One Time Programmable (OTP) Security Register

- 3*1024-Byte Security Registers with OTP Lock

128-bit Unique ID for each device

Support Replay Protection Monotonic Counter (RPMC)

- Four 32-bit Monotonic Counters

- Volatile HMAC Key register

- Non-volatile Root Key register

Fast Program and Erase Speed Typical

- 0.5ms Page program time

- 50ms 4K-byte sector erase time

- 0.16s 32K-byte block erase time

- 0.2s 64K-byte block erase time

JEDEC Standard Manufacturer and Device ID Read Methodology

Ultra-Low Power Consumption Typical

- 1uA Deep Power Down current

- 30uA Standby current

- 5.5mA Active Read current at 85MHz for STR 4IO

- 7mA Active Program or Erase current

High Reliability

- 100,000 Program / Erase Cycles

- 20-year Data Retention

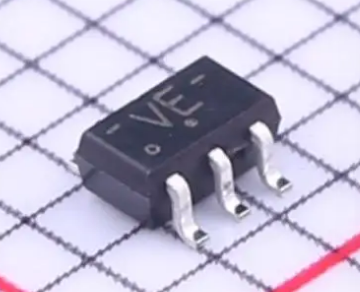

Industry Standard Green Package Options

- 8-Lead SOP (208mil)

- 16-Lead SOP (300mil)

- 8-Pad WSON(6x5x0.75mm)

- 8-Pad WSON(8x6x0.75mm)

MCU Solutions

MCU Solutions PCBA Solutions

PCBA Solutions Bluetooth Solutions

Bluetooth Solutions

FAQ

FAQ Contact Us

Contact Us

Company News

Company News Technology News

Technology News Industry News

Industry News

Company Profile

Company Profile Certificates

Certificates Terms & Conditions

Terms & Conditions Privacy Statement

Privacy Statement

Home Appliances

Home Appliances Beauty Appliances

Beauty Appliances Lighting

Lighting Kid's Toys

Kid's Toys Security Alarm

Security Alarm Health Care

Health Care